歷經(jīng)5年研發(fā)���、推翻一切舊觀(guān)念�����、創(chuàng )造未來(lái)之巔的英國dCS Varèse瓦雷茲數碼音頻播放系統�����,已經(jīng)在舉世矚目下耀目登場(chǎng)����。毫無(wú)疑問(wèn)���,dCS用令人驚訝的方式���,再次大幅拔高了原本就由自己創(chuàng )造的數碼音頻高度����,Varèse瓦雷茲的發(fā)布�,宣告了這是一套由嶄新理念與領(lǐng)先技術(shù)的完美融合���,將數碼音樂(lè )重播帶到了前所未有新紀元的旗艦產(chǎn)品���。

Varèse瓦雷茲音樂(lè )系統總共由6臺設備組成:

Varèse Core 主核心

Varèse Mono Ring DAC(2臺單聲道解碼器���,每聲道1臺)

Varèse User Control 用戶(hù)操作界面

Varèse Master Clock 主時(shí)鐘

Varèse CD/SACD Transport 轉盤(pán)(將于2024年底左右另行發(fā)布)

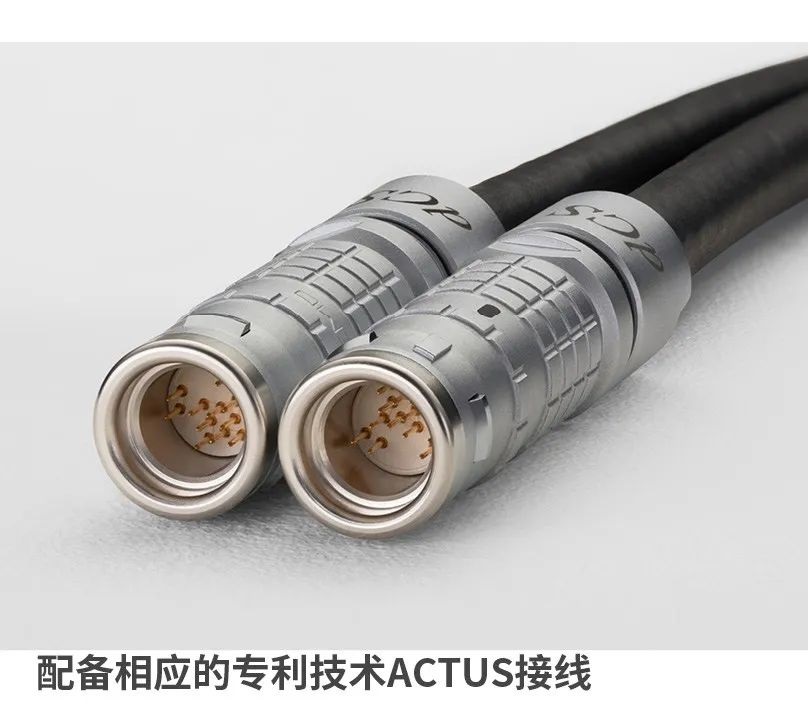

另外��,還包括1個(gè)專(zhuān)用無(wú)線(xiàn)遙控器����,配備相應的專(zhuān)利技術(shù)ACTUS接線(xiàn)����,及嶄新的應用程序:dCS Mosaic ACTUS �。

超越自我的Varèse Mono Ring DAC

Varèse瓦雷茲系統的設計始于DAC的性能革新���,創(chuàng )造性地以差動(dòng)技術(shù)開(kāi)發(fā)出Varèse Mono Ring DAC單聲道數模轉換器����。dCS Ring DAC解碼器的標志性聲音特征是精湛的低失真��,這一點(diǎn)至關(guān)重要�����,即使在低訊號電平下也是如此——這是大多數其他DAC架構所不足的領(lǐng)域����。這種卓越的超低失真性能依靠dCS從底層自研的自家Ring DAC(環(huán)形數模轉換器)�,通過(guò)自主編寫(xiě)的FPGA及獨特的電流源陣列結構��,帶來(lái)了遠超市面是現成DAC芯片的性能和聲音表現��。事實(shí)上�,Ring DAC本身極低的殘余雜訊水平��,其中絕大多數雜訊已遠遠超出了人耳可聞頻率范圍�,因此可以通過(guò)DAC輸出上溫和的模擬濾波器輕松消除�����。

在第三代Ring DAC(APEX版本)中��,每臺雙聲道Ring DAC均由96個(gè)電流源組成單端技術(shù)的Ring DAC線(xiàn)路��,其中48個(gè)用于左聲道��,另外48個(gè)用于右聲道����,構成左右聲道DAC線(xiàn)路板����。每個(gè)電流源產(chǎn)生相等的電壓��,并用于將這些電流源中的任何分量誤差(電阻值容差)作為隨機噪聲進(jìn)行分配�����?�?偣?6個(gè)電流源組成的�����。

在Varèse瓦雷茲系統中��,左聲道和右聲道被獨立成為“Mono DAC單聲道數模轉換器”�����,每個(gè)聲道獨立為一臺完整的DAC設備���。并且在線(xiàn)路技術(shù)上進(jìn)行了許多重大的改進(jìn)�����,當中包括了一些dCS專(zhuān)有技術(shù)��。每臺Varèse Mono DAC均內含了完整的96個(gè)電流源�,這意味著(zhù)每個(gè)音頻通道使用的電流源數量是第三代Ring DAC產(chǎn)品的兩倍��。這些電流源提供同步調變?yōu)?.644MHz或6.144MHz(取決于音源內容取樣率)的5Bit(位元)PCM 信號���。

Varèse瓦雷茲的Ring DAC在差動(dòng)架構中工作��;Ring DAC線(xiàn)路板上的96個(gè)電流源分為兩組���,每組48個(gè)�,其中一組以正半波轉換音樂(lè )信號�,第二組48個(gè)電流源負半波轉換音樂(lè )信號���。這意味著(zhù)反相位電流源的相位是反轉的���,并與正相位電流源相加�,并且有效抵消了信號的噪音和失真�����,從而達到更優(yōu)秀的性能和聲音表現�����。與第三代Ring DAC已經(jīng)非常出色的性能相比����,以這種差動(dòng)方式運行Ring DAC的效果提供了許多性能增強����。

差動(dòng)技術(shù)的優(yōu)勢:

1.平衡參考電源的電流消耗�。

電源基準電壓輸入到電流源��,無(wú)論接通多少電流源�����,該電壓都會(huì )乘以電流源�。除了輸入電流源的清潔直流電之外���,其他任何東西也會(huì )成倍增加�,其中Ring的正相位側處于較高電壓�,而負相位側處于較低電壓�����。這意味著(zhù)基準電源的消耗與信號無(wú)關(guān)����,因為兩組電流源工作互補����。從而消除了Ring DAC線(xiàn)路產(chǎn)生二次諧波的機制����,改善了失真性能�。

2. 改進(jìn)Ring DAC內的偶次諧波性能�。

dCS自研的Mapper映射算法規定了Ring DAC中的哪些電流源針對特定數字音頻信號開(kāi)啟和關(guān)閉����,導致正半波和負半波上的電流源產(chǎn)生不等量的開(kāi)關(guān)噪音(正半波和負半波意味著(zhù)Ring DAC在輸出端分別再生正電壓或負電壓)�。兩個(gè)反相環(huán)的差動(dòng)工作可以均衡信號正反相位的這種不對稱(chēng)性����,從而實(shí)現更優(yōu)秀的線(xiàn)性度�����。

3.均衡每個(gè)總和節點(diǎn)上的偏移�����,從而消除了顯式直流偏移校正的需要��,并提高了總和/濾波器電路的對稱(chēng)性�。

4.現有的dCS DAC采用多塊不同功能的線(xiàn)路板來(lái)執行D/A轉換過(guò)程的不同功能���,而Varèse Mono DAC則采用單一的一體化線(xiàn)路板涵蓋了所有數字處理和模擬音頻的功能�����。這在許多設計方面進(jìn)行了改進(jìn)�����,并提高了Varèse Mono DAC性能的一致性�����。

在Varèse瓦雷茲系統中����,雙單聲道DAC(每臺都運行差動(dòng)Ring DAC 架構)的工作方法�,能夠將dCS標志性的超低失真聲音推向新的性能高度�����,同時(shí)將本底噪聲降低3dB���。Ring DAC APEX已經(jīng)處于數字模擬轉換技術(shù)的前沿�����,而Varèse瓦雷茲的差動(dòng)Ring DAC繼續大大拉開(kāi)這一差距�。

電源供應的改進(jìn)

Ring DAC采用輸送到所有電流源的參考電壓�����,并將其乘以一個(gè)通過(guò)映射器輸送的數字音頻代碼樣本����,該映射器指示在任何給定時(shí)間需要打開(kāi)哪些電流源以在輸出端產(chǎn)生正確的電壓�,這意味著(zhù)DAC內部的基準電壓對系統性能至關(guān)重要�。尤其對于Ring DAC這樣具有揭示性和透明度的技術(shù)架構���,包括供電在內的任何技術(shù)細節比其它任何方案都更為重要�����。比如:在以往采用立體聲設計的Ring DAC中�����,通過(guò)比較左右聲道在不同的時(shí)間打開(kāi)和關(guān)閉不同數量的電流源會(huì )發(fā)現���。當電流源接通和關(guān)斷時(shí)��,它們相對于基準電源的阻抗會(huì )發(fā)生變化�,這可能會(huì )對基準電源產(chǎn)生波紋效應��,從而影響系統的音質(zhì)�����。APEX在此基礎上進(jìn)行了改進(jìn)���,通過(guò)降低將基準電壓輸送到Ring DAC電流源的信號路徑的阻抗���,使系統能更徹底抵抗電流源開(kāi)關(guān)和基準電源之間的這些相互作用���。

在Varèse瓦雷茲差動(dòng)Ring DAC設計中�,正反半波的電流源會(huì )以相同的方式彼此運行�,因為兩組電流源都再現相同的音樂(lè )信號(其中一組相位反相)���,基準電壓的消耗在兩者之間是相同的��。這意味著(zhù)基準電壓在工作時(shí)保持更加穩定�����,這對于像Ring DAC這樣的乘法DAC來(lái)說(shuō)��,對音樂(lè )性能有巨大的影響���。

與目前的dCS產(chǎn)品相比��,構成Varèse瓦雷茲系統電源的硬件得到了改進(jìn):Rossini和Vivaldi系統的Ring DAC采用雙電源變壓器�,DAC的模擬和數字線(xiàn)路均由單獨的變壓器供電����,從而提高了性能���,并且降低了內部的干擾�。Varèse Mono DAC毫無(wú)保留配備了雙變壓器��,而且每個(gè)變壓器都針對其在模擬或數字電源中的使用進(jìn)行了專(zhuān)門(mén)優(yōu)化���,從而提高了Mono DAC的性能和聲音重播水平���。其中電源次級電路經(jīng)過(guò)重新設計���,以減少變壓器鐵芯中的磁隙伸縮效應�����,從而消除了變壓器可能產(chǎn)生的噪聲���。電源穩壓器采用不同的拓撲結構���,電源時(shí)序通過(guò)電源管理IC實(shí)現�,以實(shí)現對電源激活和停用的更嚴格���、更靈活的控制��。為模擬信號平衡輸出級供電的電源��,也額外設計了更強大的穩壓和濾波線(xiàn)路����,以進(jìn)一步降低共模噪聲��,從而提高模擬音頻線(xiàn)路的性能�。

創(chuàng )新的ACTUS技術(shù)

在一個(gè)理想的音樂(lè )系統中���,每臺設備都能夠與系統中的其他組件進(jìn)行通信���,從而允許在它們之間發(fā)送重要信息和命令��,使系統能夠作為一個(gè)整體運行����。使用Vivaldi��,這是通過(guò)兩種主要機制實(shí)現的:3路RS232互連����,將DAC和轉盤(pán)連接到升頻器��,以及通過(guò)雙AES接口連接����。通過(guò)利用RS232連接并發(fā)送嵌入在雙AES線(xiàn)材連接中的隧道命令���,從DAC到升頻器�,以及從轉盤(pán)到升頻器��,Vivaldi系統能夠無(wú)縫控制每個(gè)組件的設置�、音量控制�����、選擇信號源等���,音頻信號也通過(guò)雙AES同步發(fā)送��。

但新的Varèse瓦雷茲系統打破了以往的觀(guān)念���。Varèse瓦雷茲采用由dCS自家開(kāi)發(fā)的定制界面����,可實(shí)現更好的音頻重播質(zhì)量——結合用戶(hù)對整套系統無(wú)縫控制的預期����。該接口稱(chēng)為:ACTUS��,音頻控制和時(shí)鐘統一系統���。ACTUS由dCS研發(fā)的專(zhuān)有硬件和軟件技術(shù)組合而成�����,允許Varèse瓦雷茲系統每部設備(核心����、用戶(hù)界面�����、時(shí)鐘����、單聲道DAC)通過(guò)各自單根線(xiàn)材連接到核心�����,包括異步數字音頻��、控制信號和主時(shí)鐘信號(通過(guò)獲得專(zhuān)利的Tomix時(shí)鐘技術(shù)發(fā)送)�,都由一根ACTUS線(xiàn)材完成連接�。

Varèse Core主核心作為系統的樞紐���,所有其他Varèse瓦雷茲設備都通過(guò)ACTUS線(xiàn)材連接到該核心����。連接器是有定位鍵的�����,這意味著(zhù)它只能以正確的方式插入�。這條線(xiàn)材本身是無(wú)方向性的��,可以在系統中的任何位置使用����,這使得使用ACTUS線(xiàn)材設置Varèse瓦雷茲系統變得非常簡(jiǎn)單��。ACTUS界面的唯一具體要求是Varèse主時(shí)鐘必須連接到Varèse Core主核心上標注「Clock」的ACTUS插座�。

ACTUS線(xiàn)材由6條雙絞銅線(xiàn)組成��,執行以下任務(wù):

1根雙絞線(xiàn)傳輸44.1k Tomix信號

1根雙絞線(xiàn)傳輸48k Tomix信號

4根雙絞線(xiàn)形成IP(互聯(lián)網(wǎng)協(xié)議)連接鏈路

IP鏈路將每臺Varèse瓦雷茲設備連接到Varèse Core主核心���。此IP鏈路使系統具有完全控制權��,允許在設備之間無(wú)縫發(fā)送信息�����、設置更改和其他控制信息����,而無(wú)需額外的控制接口��。這種控制級別對于系統故障查找也非常有用�����,例如�,系統能夠智能地通知用戶(hù)左聲道DAC未得到糾正����,或者時(shí)鐘連接到Varèse Core主核心上的錯誤ACTUS端口等等���。

IP鏈路還負責在Varèse瓦雷茲設備之間傳輸音頻信號����。ACTUS不再使用以往的AES3或S/PDIF等同步接口����,而是利用IP通過(guò)異步糾錯接口發(fā)送音頻���,這意味著(zhù)不存在時(shí)基或數據完整性錯誤的可能性��。請注意���,ACTUS不使用既定的行業(yè)標準通過(guò)IP發(fā)送音頻����,例如AES67����。

Varèse Core核心與單聲道DAC處理

對于旗艦dCS系統�,長(cháng)期以來(lái)一直使用升頻器���,這是與DAC獨立分離的一臺外置設備����,它執行超采樣過(guò)程中所需的大部分數/數轉換�、濾波和DSP��。這是dCS從開(kāi)發(fā)專(zhuān)業(yè)設備的工作中發(fā)現的��,將大量處理工作從DAC中脫離出來(lái)�,成為獨立外置設備�����,可顯著(zhù)提升效能��。

Varèse Core主核心負責處理這些元素中的大部分任務(wù)�,將DAC與必須使用的大部分數字處理工作負載脫離開(kāi)��。這意味著(zhù)大幅減少DAC內部的FPGA的工作量����,讓DAC工作更輕松��。這意味著(zhù)電源的串擾影響更少����,從而進(jìn)一步提升了單聲道DAC的性能�。Varèse Core主核心接收任何傳入的PCM源數據�,并將其超采樣至705.6或768kS/s�����,對信號進(jìn)行數字濾波以去除Nyquist奈奎斯特圖像���。然后�����,用戶(hù)可以在播放PCM源數據時(shí)選擇可選的DSD模式����。此模式將信號轉換為DSD(從標準DSD/64到DSD/512)���。然后�����,這種超采樣��、濾波的數字音頻信號通過(guò)ACTUS傳送到單聲道DAC�,并被調制為5Bit ~6MHz信號���,然后輸送到Ring DAC進(jìn)行數/模轉換�。

單聲道DAC時(shí)鐘的問(wèn)題

在時(shí)鐘方面�����,讓兩臺單聲道DAC如何能夠協(xié)調精準在同一時(shí)基上工作是相當具挑戰性的工作����。在以立體聲DAC設計的傳統數碼音頻系統中��,DAC內部就具有產(chǎn)生時(shí)鐘信號的電路�����。該時(shí)鐘信號同時(shí)傳輸到DAC的左右聲道����,這意味著(zhù)兩個(gè)聲道同時(shí)將數字音頻樣本轉換為模擬電壓��。但是����,在單聲道DAC工作時(shí)�����,DAC的所有電路都在左右聲道之間分配�����。

如果兩部單聲道DAC不能時(shí)間同步轉換左右聲道的數據��,將出現顯著(zhù)且無(wú)法接受的音頻質(zhì)量下降���。為確保數據同時(shí)轉換�����,兩臺DAC都需要確保其時(shí)鐘信號在左聲道DAC和右聲道DAC具有上升沿(構成時(shí)鐘信號的方波變化���,其中電壓從低態(tài)(如0V)變?yōu)楦邞B(tài)(如5V))時(shí)間上保持嚴格的對齊�。

但這還不夠�。即使左右聲道DAC上的兩個(gè)時(shí)鐘信號具有完全對齊的上升沿�,但是每臺DAC并非都轉換相同的數據�,出現這種情況同樣會(huì )嚴重損害音質(zhì)�����。因此�����,在時(shí)鐘方面�,兩個(gè)DAC必須精確對齊��,兩個(gè)時(shí)鐘同時(shí)產(chǎn)生一個(gè)上升沿�����,并用這個(gè)同步的時(shí)鐘信號轉換相同的數據�。而且��,目前音頻行業(yè)的解決方案(AES/S-PDIF信號同步設備)并沒(méi)有足夠的頻寬來(lái)滿(mǎn)足Varèse瓦雷茲所需的方式工作����。另一種名為AES 67的替代方案雖然有足夠的頻寬�����,但卻需要額外的時(shí)間伺服器從網(wǎng)絡(luò )時(shí)鐘重建其時(shí)鐘����。因此�,該時(shí)鐘信號的精確度性能還不如使用DAC內部的音頻速率石英晶體振蕩器生成的物理時(shí)鐘所建立的本地時(shí)鐘信號���。

專(zhuān)利Tomix時(shí)鐘協(xié)議

為了徹底解決以上問(wèn)題�,dCS決定創(chuàng )建一種新的方法來(lái)緊密同步兩臺單聲道DAC的時(shí)鐘����,同時(shí)利用每臺DAC內部基于VCXO(壓控晶振元件)的本地高質(zhì)量時(shí)鐘電路來(lái)控制各自的Ring DAC電路�����,從而更大限度地提高系統��。從而誕生的解決方案是Tomix時(shí)鐘協(xié)議����。

Tomix是一種定制的專(zhuān)利方案����,Varèse Core主核心的作用與傳統音頻系統中的主時(shí)鐘大致相同�����。它將時(shí)鐘信號發(fā)送到兩個(gè)單聲道DAC上��,它們會(huì )同步這兩個(gè)單聲道DAC���,從而確保DAC時(shí)鐘以相同的速率運行�。然而�����,這本身并不能解決保持D/A轉換同步的問(wèn)題���。

Core是Varèse瓦雷茲系統的中心�����,任何音頻和時(shí)鐘信號始終通過(guò)它:無(wú)論源�、系統配置和設置如何�����。在通過(guò)ACTUS將數碼音頻數據發(fā)送到DAC之前���,Core會(huì )為通過(guò)它的每個(gè)音頻數據添加一個(gè)時(shí)間戳�。當數據到達DAC時(shí)��,DAC內的FPGA會(huì )顯示時(shí)間戳�。然后���,DAC確切地知道數據的發(fā)送時(shí)間�����,但為了確保在正確的時(shí)間將數據轉換為模擬信號����,它還需要確切知道當前的時(shí)間基準�。這就是Tomix時(shí)鐘協(xié)議的用武之地�。時(shí)鐘信號加蓋時(shí)間戳的方法對音頻性能至關(guān)重要����。Tomix信號由Varèse主時(shí)鐘生成���,或者如果系統中未使用主時(shí)鐘����,則由Varèse Core主核心產(chǎn)生��。技術(shù)的成果令人欣喜���,Tomix時(shí)鐘協(xié)議是dCS一種獲得專(zhuān)利的技術(shù)���,讓Varèse Mono DAC具有精確同步的時(shí)鐘����,確保單聲道Ring DAC在完全相同的時(shí)間轉換左聲道和右聲道的音頻數據�����。